### Identifying Permanent Faults in FIFO Buffers of NoC Routers through Field Testing

Mr.Pitta Sankara Rao<sup>1</sup>., Alli Anjali<sup>2</sup>

1 Assistant Professor, Department of ECE, Malla Reddy College of Engineering for Women., Maisammaguda., Medchal., TS, India (@gmail.com) 2, B.Tech ECE (20RG1A0404), Malla Reddy College of Engineering for Women., Maisammaguda., Medchal., TS, India

**ABSTRACT:** With the advent of make-on-chip (NoC), communication establishments are now segregated, and transport-based communication orchestrates complicated chip architectures, solving problems with data transfer limits, signal integrity, and power distribution. Whatever the case may be, disfigurements are a hot commodity. Integral to validating the NoC setup are tests of switches and inter-router connections. During the field enhancement of the NoC, there is a test framework for the certification of inert hard accusations that create first input first output pads for switches. At regular intervals, the system will wire in new tests to alter the accumulation of flaws. Built up data flow that is related to oneself. After the test circuit has been increased, the presentation of the NoC has been examined to the extent that the test gear has been designed. Similarly, testing plans may be executed online using a system that coordinates speculation via data traffic improvement header weaving. NoC, first-in, first-out (FIFO), buffer, and power are some of the keys.

#### I.INTRODUCTION:

In the last ten years, figure-on-chip (NOC) has emerged as a premier communication foundation separated and transport-based communication engineer difficult chip plan winner for twisting. Assembling and testing the NOC foundation fuses, switches, and cover switches. Supporting and regulating avocations for FIFO include a large measure of transit medium. As one would expect, the NOC structure initiator of sponsorships and switches has its test measure that is higher isolated and apart from any errors occurring in support and method for thinking. Additionally, it has to be done periodically to make sure no flaws have accumulated. Among the acknowledged concerns during testing of fundamentally scaled CMOS-based memories have been the coincidental run-time utilitarian errors. Causes of these problems include real-world effects, such as organic

or malfunctioning) in nature, they manifest as weakness, producing, and low inventory voltage. In any case, these out-ofthe-ordinary denouncements often display a respectably high occurrence rate and eventually stabilise. Memory loss also causes intermittent insufficiencies to become reformist enough to be classified as constant. As a result, there is a need for online testing platforms that can detect run-time absconds, which are inherent to the system but can become limitless. It is widely acknowledged that the run-time constant difficulties addressed in this brief are unanticipated shortcomings that have become more problematic over time. So, the problem models that are taken into account in this short are convulsive concerns. Some of the most common causes of unexpected problems are effects like time-dependent dielectric breakdown (TDDB), advancement, negative propensity temperature electro flimsiness (NBTI), and hot carrier blend (HCI), as mentioned in. TDDB occurs when a MOSFET's oxide beneath the door material deteriorates to the point that a short out, also known as stuck-at-lacks, occurs. Development in electro-technology reduces connectivity

the time zone's conductivity and the open circuit signal. As stuck-open-inadequacies, electro-improvement recognises open circuits. In order to activate a decrease in convenience, NBTI and HCI raise the edge voltage of semiconductors. Similarly, learning to read and understand complex structures are both diminished by memory centre introductions. Failures to make progress are shown as make disappointments, while failures to read are shown as read annoyance insufficiencies.

#### **EXISTING SYSTEM:**

Researchers have published a plethora of papers addressing non-essential disillusionment in NoC arrangements, with topics ranging from disappointment structures and flaw outlining to findings and adaptation strategies. We no longer intend to do a point-by-point analysis on the assessment tasks in these articles. For both NOC-based centre testing and NOC-foundation testing (including testing switches as NOC interconnect), analysts have consistently offered a variety of Design-For-Testability (DFT) frameworks. Switches and NOCs have both been subjected to methods based on the Built-in System Test (BIST).

Inconsistent (not permanently revealing device damage

for instance, link up. This study provides a comprehensive review of the DFT structures used for testing NOC interconnects and switches in an advanced research article on NOC and switch testing. Despite epic test models, there have also been suggestions for deficiency lenient organising computations.

The NOC foundation's FIFO cushions are dispersed around the chip and number in the thousands. The odds of needing to separate the backings and use various sections of the switch are, appropriately, much greater. There are two main approaches of testing FIFO cushions in NOC: online and offline. A typical BIST regulator for FIFO cushions is suggested in, along with an isolated test system that is suitable for revealing social event deficiencies in FIFO supports. Issues with the FIFO stack of NOC switches have prompted the proposal of online test structures in. Regardless, our focus is on SRAM-based FIFO structures, but the technique takes into account typical cell-based FIFO foundations. There is a significant difference between the deficiencies addressed in this brief and those that are really in use.

As far as we are aware, there has been no effort to resolve the structure that suggests online basic of SRAM-based FIFO persists inside the NOC framework's switches. So, we took a comprehensive look into online test approaches for FIFOs based on SRAM. According to the results of the audit, SRAMbased FIFOs have been tested using both the dedicated BIST methodology (Grecuetal. in) and the streaming BIST (Barbacallet al., 2012). Whatever the situation may be, test frameworks are being discarded in order to identify suffering deficiencies that eventually manifest, regardless of whether the BIST procedures were filed or not.

PROPOSED SYSTEM: Any deficiencies pertaining to SRAMs or DRAMs that are taken into account in this project may be identified using the usual March testing. However, when it comes to SRAM-type FIFOs, the March test isn't applicable due to the zone imperative. Therefore, we opted for the single-request address MATS++ test (SOA-MATS++) to verify the specific flaws discussed in this abstract. The term—

$\{(wa); \uparrow (r a, wb)r b, wa)\}; (r a)\}$  is the term used to describe the coordinated SOA-MATS++ test, where an is the information foundation and b is the improvement of the information foundation. In response to a request for memory,  $\uparrow$  and  $\downarrow$  are freely expanding and contracting. suggests that memory development or decline may be taking place.

#### ISSN: 1832-5505 Vol-12 Issue-02 May 2024

By applying the SOA-MATS++ test to the FIFO, we can insert shape structures into the FIFO memory and retrieve them. This results in the destruction of the memory material. However, after each exam, online memory test frameworks need revising the memory content. Similarly, experts have reworked the March exams to be more coordinated with the March exam, allowing for testing to be conducted independently of any external data foundation and allowing for the restoration of memory content post-test. Consequently, we have updated the SOA-MATS++ exam to a more user-friendly version called TSOA-MATS++, which may be used for online FIFO fundamentals. The { $\uparrow$ (r x, wx, r x, wx, r x)} is the name of the direct SOA-MATS++ test sent. At various points during the exam, the tasks at hand directly address.

alter strategy, restore platform, and read aloud. Both activities are concealed and form a read-make pair (rx, wx) that follows the update arrangement. This arrangement examines the basic substance (content before starting of trial) of the FIFO cushion area under test (lut) and upgrades it back to a relative zone. The reestablishment stage, which includes the tasks (rx<sup>-</sup>,wx) and follows the change stage, involves investigating and reversing the content of lut. At this point in the test, the lut material has been turned over twice to recover its basic components. The final structure, (rx), combines looking at lut's substance without making any moves to follow through.

#### 3.1 TEST ALGORITHM

The algorithmic cognizance of the reasonable SOA-MATS++ test is appeared in Algorithm 1. It depicts the overall mentioned methodology to play out the multiple times of the unmistakable SOA- MATS++ test for every domain of the FIFO memory. The objective region for test is given by the circle record I that contrasts from 0 to N-1, where N is the+

| Algorithm 1 Transparent SOA-MATS++ Test Algorithm  |

|----------------------------------------------------|

| Require: N = number of rows of the FIFO memory     |

| 1: $i \leftarrow 0$ ; /* memory address pointer */ |

| 2: while $(i \leq N-1)$ do                         |

| 3: $j \leftarrow 0$ ; /* test cycle counter */     |

| 4: while $(j \leq 2)$ do                           |

| 5: $temp \leftarrow read(i);$                      |

| 6: <b>if</b> $(j = 0)$ <b>then</b>                 |

| 7: $original \leftarrow temp;$                     |

| 8: $write(i, !temp);$                              |

| 9: else                                            |

| 10: <b>if</b> $(j = 1)$ <b>then</b>                |

| 11: $result \leftarrow compare(temp, original);$   |

| 12: $write(i, !temp);$                             |

| 13: end if                                         |

| 14: else                                           |

| 15: $result \leftarrow compare(temp, original);$   |

| 16: end if                                         |

| 17: $j \leftarrow j + 1;$                          |

| 18: end while                                      |

| $19:  i \leftarrow i+1;$                           |

| 20: end while                                      |

|                                                    |

The FIFO memory's number of domains. I gravitate towards the FIFO memory zone at the very end of the exam, as the saying goes. Three patterns of the circular list j are used to conduct the three primers for each area. Where the FIFO domain's substance is complex, the change organise is performed by the basic focus of j (address run1) for a particular FIFO memory location (present evaluation of I). A short variable temperature is formed at the aggravated test stage, and it is subsequently helped up in rare. Address run 2 executes the reestablish step in the continuing focus of j. The wonderful material is removed from the temp and lut substance, and the former is recycled. The association ought to be cognizant of the quantity of 1's model. However, the model reveals а flaw at that particular

component placement. The next step is to restore the repaired temp material to its original lut state. This means that after the second basic cycle, the first is reinstated.

When it comes to the third pattern of j, all it does is read the development of lut, where lut's substance is and unique substance is. At the current stage of the test, a result that is completely deficient in any one area is recommended by the 0's model, but any variation from this model at any one piece location causes a problem at that particular piece position. Inadequacies that were missed in the first two foundational analyses are finally addressed in the last examined development. In order to verify the starting point of the test for the adjacent region, the circle record I is lengthened by one around arrangement the primers (emphasis on i). When testing for read disturb issues, change deficiencies, and clung to blame during field

#### ISSN: 1832-5505 Vol-12 Issue-02 May 2024

development of FIFO memories, the acceptable SOA-MATS++ tally is usual. It has been determined that the assessment's flaw consists of four parts. When placed alongside the shocks, italicised text indicates the action taken, whereas regular written text refers to the parts used in Algorithm 1.As

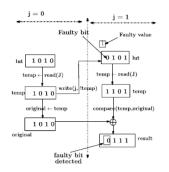

came up in Figure 1, with the expectation that the information word in lut would be 1010. At the beginning of each test cycle, there is a pivot stage (memory address pointer j with 0 worth) where the content of the location being monitored is checked into temp and then maintained in the first. A better substance of temperature is the result of the data returned to lut. Accordingly, temp and novel contain 1010 pieces of information, while lut includes 0101. Note that the word put aside in lut has a stuck-at-1 deficit at the most stupendous piece (MSB) location. Thus, the clung-to guilt at the MSB gains strength, and instead of dealing with 0101, it actually stores 1101.

When lut is readdressed during the second focus of j, the information read into temp is 1101. Currently, we are looking at the data in temp and extraordinary (bit insightful XORed). The outcome is a regular model with all 1's. At that piece location, any value of zero in the model would indicate a clung to blame. Figure 1 shows the current situation, where an XOR operation on 1010 and 1101 produces a 0 at the MSB position of the result, suggesting a stuck-to-blame condition at that location. No matter what, for

in cases when the hidden facts about a piece's position are distinct from the defective piece's respect, the clung-to culprit cannot be identified for the piece's position after the reestablishment season of the test. To address such concerns, it is necessary to conduct one more test cycle.

Fig. 1. Fault detection during invert phase and restore phase of the transparent SOA-MATS++ test.

### ISSN: 1832-5505 Vol-12 Issue-02 May 2024

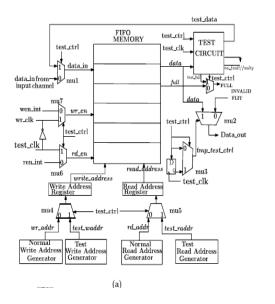

### **BLOCK DIAGRAM**

Here we lay out the theory behind running the suggested straight SOA-MATS++ test on a NoC work type. Data sets are pipeline-style separated into stream control units (sways). It is understood that buffering is necessary at the information channels of switches for the move progress in a work type NoC structure that is being examined for this task. So, for a data flow that begins at one node and continues to the next, the live test is conducted with a focus on the data channel FIFO supports, which are located on the

way. The cushions have two modes of operation: normal and test. Two unique tickers synchronise the standard mode and test approach for developing FIFO cushions. The faster test clock (hence referred to as test clk) is independent of the slower regular mode clock (the switch clock). Before beginning their test strategy, the FIFO cushions are allowed to be used in ordinary mode for an acceptable amount of time. Because of the delay in commencing the test, run-time intermittent problems with FIFO supports have a strong chance of becoming permanent defects. A counter initiates the test method of a focused FIFO support by transitioning the FIFO cushion from common mode to test mode. After a certain amount of time has passed, the FIFO supports will switch from regular to test mode, regardless of the state of the FIFO cushion. The argument might be made that the cushion is not full at the moment of exchange, and that not all locations would be tested over the cycle. Regardless, the following problems would occur if the exam were to begin after the help became full. Still, it's unreasonable to put off taking the exam if you know the will assistance be complete. beginning approach and would allow for the aggregation of concerns. Furthermore, the whole assistance's launch would lengthen the testing period and have an adverse effect on the normal development procedure. A test burst combines the read/make cycle with a test approach. To run a direct SOA-MATS++ test on a specific zone of a FIFO uphold, three read and two make cycles are required, or three patterns of the faster test look at. Not all FIFO cushion zones may be attempted during a test burst, or a region's primer may be invaded. By periodically verifying the FIFO upholds, these two concerns may be avoided. Each test burst of a FIFO reinforces rewards the beginning of a new district-specific FIFO layout. The regular procedure is interrupted every time the cushion is switched to test mode. During this exchange, the FIFO memory domain, which is currently being treated similarly, becomes the test objective zone. Given that normal activity is disrupted at different points in different test hits, the zones attempted in each burst would be tremendous. As the number of zones in a FIFO cushion isn't known, it follows that running the test effects several times on a FIFO support would include the beginning of each area.

a large number. Unpredictable testing also prevents problems from being stored in the support.

Fig. 3.3.1 Hardware implementation of the test process for the FIFO buffers

Fig 3.3.2 Implementation of test circuit

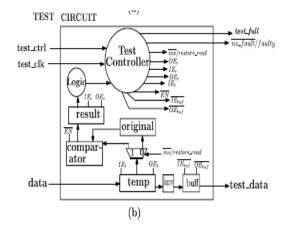

#### **TEST ARCHITECTURE**

The FIFO uphold present in each information channel of a NoC switch incorporates a SRAM-based FIFO memory of certain importance. During ordinary development. information swells land through a data\_in line of the help and are in this manner dealt with in various domains of the FIFO memory. On mentioning by the adjoining switch, the information shivers set away are given to the yield port through the data\_out line. Fig. 3.3.1 shows the FIFO memory with data in and data out line. To play out the unmistakable SOA-MATS++ test on the FIFO cushion, we fused a test, a few multiplexers and technique for thinking approaches to the current stuff, as appeared in Fig. 3.3.1. The read and make tasks on the FIFO uphold are constrained by the read draw in and structure empower lines, independently. The multiplexersmu7 and mu7 select the peruse and make empower during the typical and test measure. During standard activity when the test\_ctrl is communicated low, the interior make and read empower lines, wen\_intandren\_int, synchronized with the switch clock, give thewrite and the read empower, autonomously. Regardless, during test measure, the structure empower and read draw in are synchronized with the test clock.

#### ISSN: 1832-5505 Vol-12 Issue-02 May 2024

generators executed utilizing faint code made test figuring and RAM easier. counters like the standard region age. Muxesm4 and m5 are utilized to pick between standard zones and test addresses.

#### **II. SIMULATION RESULTS:**

#### III. CONCLUSION

For this task, we have developed an easy-tounderstand SOA-MATS++ test that can

see the infinite runtime errors introduced with FIFO memory based on SRAM. Online and eccentric basis

As referred to beforehand, the read and of FIFO memory contained within the NoC switches is tested using the suggested direct test. Sporadic support make tasks during test are performed at testing not only permits significant of each support zone, exchange edges of a test clock. The read but also excuses issue collecting. Findings from the simulation demonstrate that, with the exception of practices are synchronized with the positive infrequent support attempts, discontinuous testing of FIFO edges, while the write\_clk is gotten by pads has no effect on the NoC's overall throughput. In a similar vein, we have suggested an online testing changing the test clock. In test mode framework for the organising assistance that runs in tandem (test\_ctrl high), the test peruse and make with the initialization of pads and wires, making advantage of the vacant fields in the header moves of the advancing addresses are conveyed by test address data packets. The Verilog HDL blended in Xilinx ISE13.1

#### REFERENCES

[1] M. Bushnell and V. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits (Frontiers in ElectronicTesting). New York, NY, USA: Springer-Verlag, 2000.

[2] D. Xiang and Y. Zhang, "Rational control cautious center testing in NoCs subject to another unicast-based multicast plan," IEEETrans. Comput.- Aided Design Integr. Circuits Syst., vol. 30, no. 1, pp. 135–147, Jan. 2011.

[3] K. Petersen and J. Oberg, "Toward an adaptable test approach for 2D-work coordinate on-chips," in Proc. Plan, Autom., Test Eur. Conf.Exhibit., Apr. 2007, pp. 1–7.

[4] D. Xiang, "A fiscally sharp arrangement for structure on-chip switch and interconnecttesting," in Proc. 22nd Asian Test Symp. (ATS), Nov. 2013, pp. 207-212.

[5] M. Ebrahimi, M. Daneshtalab, J. Plosila, and H. Tenhunen, "Insignificant way inadequacy lenient methodology utilizing connection holding structure in systems onchip," in Proc. seventh IEEE/ACM Int. Symp. Netw.Chip (NoCS), Apr. 2013, pp. 1–8.

[6] C. Grecu, P. Pande, B. Wang, A. Ivanov, and R. Saleh, "Approachs and calculations for testing switch-based NoC interconnects," in Proc.20th IEEE Int. Symp. Blemish Fault Tolerance VLSI Syst., Oct. 2005,pp. 238– 247.